在Verilog编程中,错误代码的出现是开发者必须面对的挑战之一,错误代码10240是一个相对常见的错误,它通常涉及到寄存器或信号的位宽定义问题,本文将详细介绍错误代码10240的产生原因、识别方法、解决方案以及相关的注意事项。

Verilog错误代码10240解析

在Verilog编程中,错误代码10240通常表示位宽定义不一致,当你在模块内对一个信号或寄存器进行位宽定义时,如果在某处未正确地指定其位宽,编译器就会报出错误代码10240,这种错误可能会导致仿真结果不正确或硬件描述不符合预期。

识别方法

要识别错误代码10240,首先需要查看编译器给出的错误信息,错误信息会指出出现问题的文件及具体行数,在此基础上,检查相关代码,特别是涉及到位宽定义的部分,注意以下几点:

1、检查信号和寄存器的位宽定义是否一致。

2、查看是否有未指定位宽的信号或寄存器。

3、检查连接端口(port)的位宽定义是否正确。

解决方案

针对错误代码10240,可以采取以下解决方案:

1、确保所有信号和寄存器的位宽定义一致,在模块内,每个信号和寄存器都应具有明确的位宽定义。

2、为未指定位宽的信号或寄存器添加位宽定义,在声明时,确保为每个信号或寄存器指定正确的位宽。

3、检查并修正连接端口的位宽定义,确保模块间的连接端口位宽匹配。

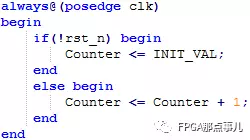

以下是一个简单的示例,展示了如何解决错误代码10240:

错误示例(可能导致错误代码10240):

module test; reg r; // 未指定位宽 wire [7:0] w; // 正确指定了位宽 ... endmodule

修正后的示例:

module test; reg [7:0] r; // 指定了正确的位宽 wire [7:0] w; // 保持正确的位宽定义 ... endmodule

注意事项

在解决Verilog错误代码10240时,需要注意以下几点:

1、仔细核对代码中的每一个信号和寄存器的位宽定义,确保一致性。

2、在进行模块间通信时,确保连接端口的位宽匹配,避免出现不匹配的情况。

3、在设计过程中,尽量避免使用不确定位宽的信号或寄存器,以减少出错的可能性。

4、在修改代码后,重新编译并仿真,以验证是否解决了错误代码10240。

Verilog错误代码10240是一个与位宽定义有关的常见错误,本文详细介绍了该错误的产生原因、识别方法、解决方案以及注意事项,通过遵循本文的指导,读者应能够有效地解决Verilog编程中的错误代码10240问题,从而提高代码的质量和仿真结果的准确性,在实际开发中,建议读者养成良好的编程习惯,如及时保存代码、定期备份等,以便在遇到问题时能够快速定位并解决,不断学习和掌握Verilog编程技巧也是提高开发效率的关键。

京公网安备11000000000001号

京公网安备11000000000001号 京ICP备11000001号

京ICP备11000001号

还没有评论,来说两句吧...